30+ system verilog analog modeling

VLSI circuit design tool with connectivity at all levels. I have a wide range of skills to make this happen including.

What Is Verilog Code For 8 Bit Led Display Quora

SaunaSINDA Cold plate integration TECs Vapor.

. As an agile team member understanding the requirements implementing robust code creating unit tests and helping to automate as much of the SDLC as possible to make sure we can continually improve and deliver better quality with faster speed. The VHSIC Hardware Description Language VHDL is a hardware description language HDL that can model the behavior and structure of digital systems at multiple levels of abstraction ranging from the system level down to that of logic gates for design entry documentation and verification purposesSince 1987 VHDL has been standardized by the Institute of Electrical and. Model system logic using state machines flow charts and truth tables.

Name Architecture License Autorouter Comment Electric BSD Java. Verification techniques and languages such as co-simulation System Verilog and OVMUVM. State transition tables provide a structured environment for modeling state machines in Simulink.

Tuesday May 17 930 am 800 pm with morning and afternoon breaks a buffet lunch. FreePCB allows for up to 16 copper layers both metric and US customary units and export of. Verification IP implementation TB developers.

Verilog is a widely used Hardware Description Language HDL for designing digital circuits. Ho Chi Minh Job Description. In this circuit the MOSFET converts variations in the gate-source voltage into a small signal drain current which passes through a resistive load and generates the amplified voltage across the load resistor.

EMA3D Cable bolsters the design-to-validation workflow with system-design evaluation for cable harness models in the aerospace automotive military oil and gas consumer electronics and energy. Can also be used for schematic entry and PCB design. Check them out and good luck.

Circuit design analog digital power electronics and RF Circuit board PCB layout using Eagle KiCAD and PADS Circuit debugging testing and troubleshooting Soldering manual hot-air and reflow for assembly and rework Embedded programming in C Arduino and. Destructive and Non-Destructive Effects. A Verilog model describes a unit of digital hardware in terms of.

First a brief overview of. Verilog Analog and Digital CMOS design and Digital Electronics. JEDEC component thermal models Statistical estimation of circuit heat dissipation ECADMCAD data exchange CFD simulation and boundary conditions Multi-physics simulations Temperature management Determining heat and temperature distributions in PCBs Metal core CCAs Resistance network thermal modeling eg.

He also holds a Post-Graduate Diploma in Embedded System Design from the Centre of Development of Advanced Computing Pune India. Generate VHDL and Verilog code for FPGA and ASIC designs with HDL Coder. While it can also handle systems that process other types of signals it is not efficient for.

It can also be used for modeling analog circuits. By implementing Ansys Twin Builder you can improve top-line revenue manage bottom-line costs and both gain and retain a competitive advantage. CT Analog Verilog-A is designed to allow modeling of systems that process continuous time CT signals.

2-5 years Job Location. Behavioral Modeling modeling the design. Figure below shows the common source amplifier circuit.

Hybrid digital twins enable system design and optimization and predictive maintenance and they optimize industrial asset management. In this manuscript recent progress in the area of resistive random access memory RRAM technology which is considered one of the most standout emerging memory technologies owing to its high speed low cost enhanced storage density potential applications in various fields and excellent scalability is comprehensively reviewed. Ansys Fluent is the industry-leading fluid simulation software known for its advanced physics modeling capabilities and industry leading accuracy.

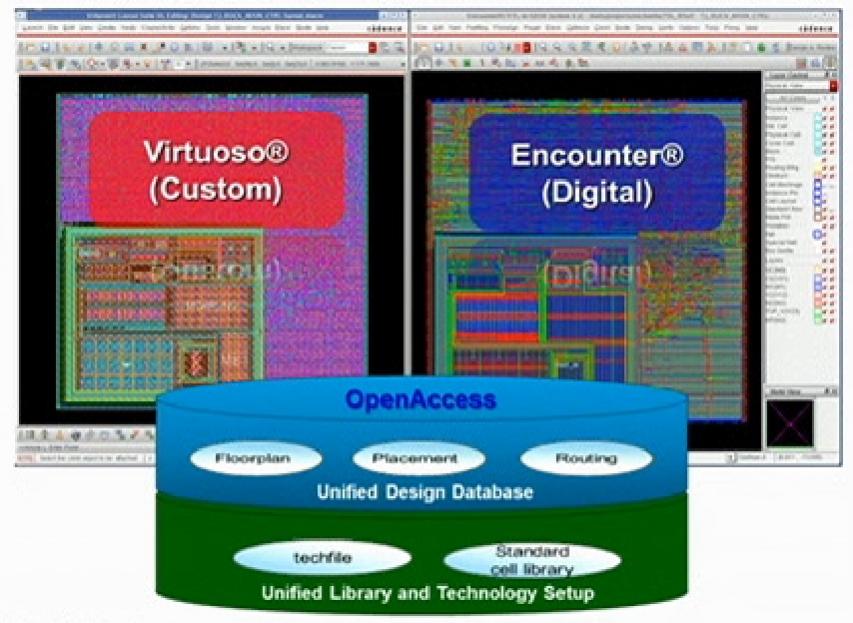

Verilog is a descriptive language that describes a relationship between signals in a circuit. A printed circuit board design program for Microsoft Windows. Functional view generation for all the analog and mixed signal modules used in the chip Cadence Netlist generation using C-Core and Virtual Core for 5 projects in the span of two years.

Simulation speed-up techniques emulation new tools and methods for design validation. Basic Mechanisms and Modeling. Flash Type ADC is based on the principle of comparing analog input voltage with a set of reference voltages.

To convert the analog input voltage into a digital signal of n-bit output 2 n 1 comparators are required.

How Is Concurrency Achieved In A Verilog Simulator Quora

Which Training Is The Best Among Verilog Virtuoso Vhdl And Pspice For The Best Future In The Vlsi Field Quora

Boost Analog Design Model Accuracy Electronic Design

What Are A Few Verilog Codes That A Design Engineer Should Know Quora

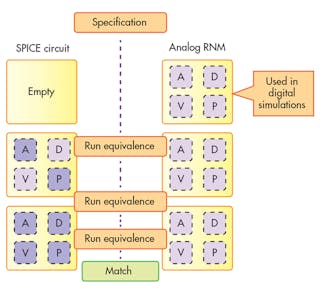

Make The Move From Module Based Mixed Signal Verification To Uvm Electronic Design

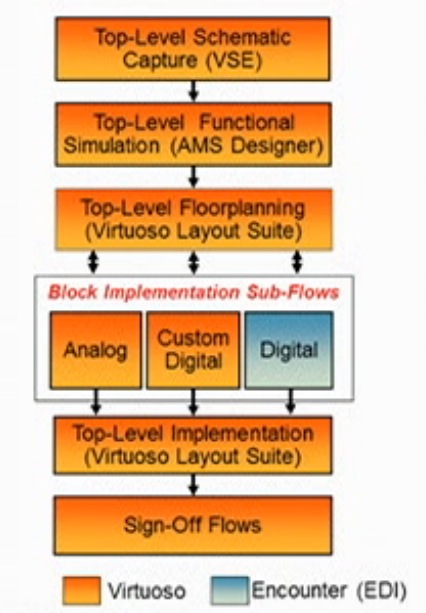

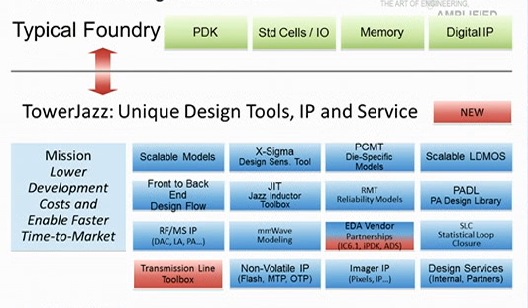

An Ams Reference Flow For Power Management Designs Semiwiki

An Ams Reference Flow For Power Management Designs Semiwiki

The Growing Uncertainty Of Sign Off At 7 5nm

Modern 2010 Review Eniac Modern Ref Technical Annex Modern Partb Rev2 V3 3 Wp1 Giuliana Gangemiwp2 Andre Juge Wp3 Wilmar Heuvelmanwp4 Davide Ppt Download

Which Verilog Simulator Is Mostly Preferred In The Industry Quora

Make The Move From Module Based Mixed Signal Verification To Uvm Electronic Design

How Are Verilog A And Verilog Ams Different Quora

Boost Analog Design Model Accuracy Electronic Design

How To Design An N Bit Register Which Stores Randomly Generated Numbers In Verilog Xilinx Quora

Boost Analog Design Model Accuracy Electronic Design

Boost Analog Design Model Accuracy Electronic Design

An Ams Reference Flow For Power Management Designs Semiwiki